# Fredrik Robertsén

# The Lattice Boltzmann Method, a Petaflop and Beyond

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 231, April 2018

### The Lattice Boltzmann Method, a Petaflop and Beyond

Fredrik Robertsén

To be presented, with the permission of the Division of Natural Sciences and Technology of the University of Åbo Akademi for public criticism in Auditorium XXI on April 20, 2018, at 13.

> University of Åbo Akademi Department of Information Technologies Vattenborgsvägen 3 20500 Åbo Finland

> > 2018

### **Supervisors**

Professor Jan Westerholm Department of Information Technologies Åbo Akademi University Vattenborgsvägen 3 20500 Åbo Finland

Docent Keijo Mattila Faculty of Mathematics and Science University of Jyväskylä Survontie 9 C Finland

### Reviewers

Professor Erik Lindahl Department of Biochemistry and Biophysics Stockholm University Universitetsvägen 10 A, 106 91 Stockholm Sweden

Dr. Derek Groen Department of Simulation and Modelling Brunel University London Kingston Ln, London, Uxbridge UB8 3PH United Kingdom

### Opponent

Professor Erik Lindahl Department of Biochemistry and Biophysics Stockholm University Universitetsvägen 10 A, 106 91 Stockholm Sweden

ISBN 978-952-12-3692-1 ISSN 1239-1883

### Abstract

With computer simulations real world phenomena can be analyzed in great detail. Computational fluid dynamics, for example, allows simulation of fluid flow phenomena that might not otherwise be observable or researchers might not have the resources to observe. Researchers want to analyze larger and more complex systems in a shorter time to allow them to get more work done with their resources. To achieve this the simulation codes need to be able to efficiently use large computer systems.

This thesis focuses on the lattice Boltzmann method (LBM) and the usage of computational accelerators to run LB simulations, but also covers some optimization and performance results for regular CPU based systems. The higher memory bandwidth of the computational accelerators has a significant impact on the performance of the LB code, allowing the accelerators to easily outperform contemporary CPU systems.

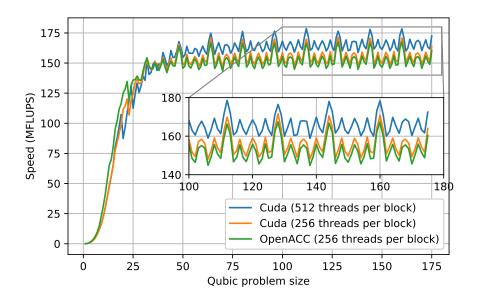

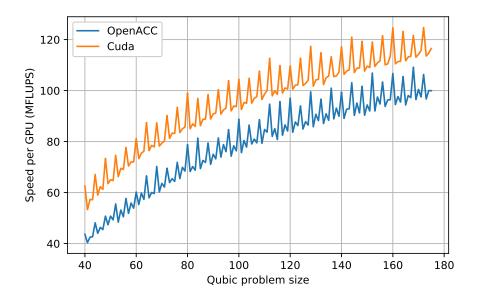

The hardware architectures of HPC systems used for these kinds of simulations are briefly presented, as well as what programming methods can be used for these systems. This thesis examines how the usage of the OpenACC programming standard makes it easier to create GPU programs. The benefit of OpenACC compared to CUDA is that it allows the user to add directives into the code. These directives control what part of the execution will be offloaded to the accelerator. In this thesis, there is a description of how OpenACC directives can be applied to an LB solver. We also include a comparison of the performance of that OpenACC solver with a native CUDA solver, both implemented using the same optimization techniques.

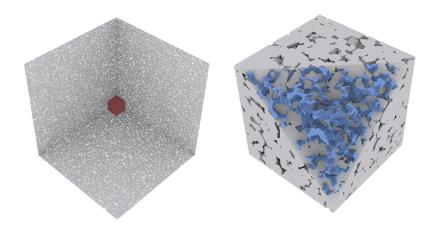

For large-scale GPU accelerated systems it is important that any program running on them is able to efficiently utilize the resources. In this thesis, we examine the performance achievable on large-scale GPU accelerated systems running lattice Boltzmann simulations. Specific attention is given to the scalability of our GPU accelerated LB solver on the Titan supercomputer, running on 16384 GPUs in parallel. The highlight of these simulations shows that porous media fluid flow simulations on this system can achieve over 1 petaflops of sustainable computational performance. Basic implementation details such as data layouts and algorithms used are also covered, and the impact they have on the performance is discussed. The results from the large scales simulations show that, even with rather homogeneous porous media samples the workload can become unevenly distributed among the computing units. In this thesis we demonstrate that even a simple recursive bisection scheme, a particular domain decomposition scheme, can effectively improve the load balance for the porous media case used.

The solver used on Titan is implemented using asynchronous communication. This is done to allow the GPUs to continue working uninterrupted while the communication takes place. This thesis discusses how asynchronous communication is handled on GPU systems and the steps needed to allow asynchronous communication while still maintaining memory access patterns that are well suited to the GPU.

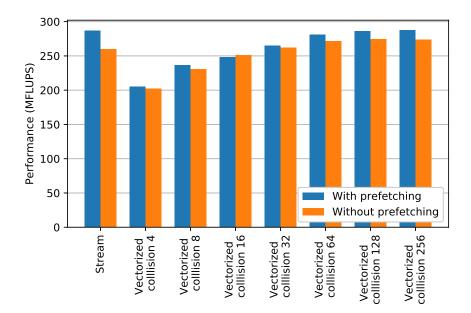

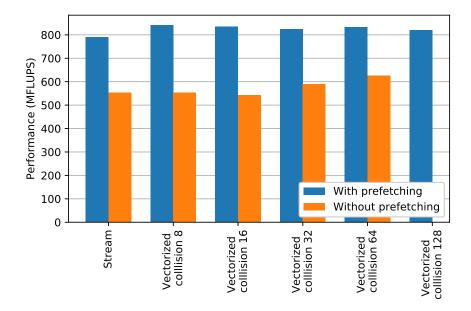

Finally, newer processors are deriving more and more of their computational power from SIMD vectorization. The thesis examines the effects vectorization has on an LB solver running on a regular Intel Xeon processor and the manycore Xeon Phi processors. This includes an in-depth analysis of the key optimization methods applied to the code for the Xeon Phi processor. Most of the key optimizations center around how the fast, on-package memory is used. Design choices, such as the data layout and the addition of manual prefetching instructions into the program increases how efficiently the memory bandwidth can be utilized.

### Sammanfattning

Denna avhandling fokuserar på lattice Boltzmann metoden (LBM) och hur beräkningsacceleratorer används för att uppnå en hög prestanda för denna typ av simuleringar. Optimeringstekniker för LB simuleringar som körs på normala CPU-baserade system diskuteras också. Den högre minnesbandbredden tillgänglig på beräkningsacceleratorer leder till att kod som kör på dessa lätt klarar av att leverera en högre prestanda än samtida CPUbaserade system.

I avhandlingen presenteras kort hårdvaruarkitekturen som används på dessa typer av högpresterande datorsystem och vilka programmeringstekniker som kan användas för dessa system. En programmeringsteknik som diskuteras mera ingående är OpenACC standarden. OpenACC gör det lättare för programmeraren att skapa kod för beräkningsacceleratorer genom att lägga in direktiv i programkoden. Direktiven beskriver för kompilatorn vilka delar av koden som skall avlastas till beräkningsacceleratorer och hur denna avlastning sker. Denna avhandling demonstrerar hur OpenACC direktiv läggs till ett LB program och jämför prestandan denna version kan uppnå med prestandan av ett CUDA program implementerat med samma metoder.

Stora accelererade datorsystem som använder grafikprocessorer börjar bli allt vanligare. Eftersom skalbarhet är viktigt för stora system, undersöker vi hur vårt accelererade LB simuleringsprogram kan köras på Titan superdatorn på 16384 grafikprocessorer. Resultaten från dessa simuleringar visar att LB simuleringar för poröst material klarar av att prestera över 1 biljard flyttalsoperationer per sekund. Hur grundläggande implementationsdetaljer så som hur data ordnas i minnet och olika typer av algoritmer påverkar prestandan diskuteras också. Dessa storskaliga simuleringar visar att även om dessa porösa material ofta har en homogen struktur orsakar strukturen en obalans i belastningen mellan beräkningsnoder då simuleringarna distribueras över tusentals beräkningsnoder. För att minska denna obalans implementerade vi en rudimentär algoritm för att bättre distribuera belastningen i systemet.

Programmet som kördes på Titan superdatorn var implementerat så att kommunikationen mellan beräkningsnoder kunde genomföras asynkront. Denna asynkrona kommunikation låter grafikprocessorerna fortsätta jobba samtidigt som data kommuniceras med andra relevanta beräkningsnoder i systemet. I avhandlingen diskuteras hur asynkron kommunikation hanteras på system med grafikprocessorer. Samtidigt diskuteras hur uppdelningen av beräkningsdomänen lellan grafikprocessorerna skall göras för att låta programmet fortfarande läsa och skriva data i ett mönster som är optimalt för grafikprocessorer.

Nyare processorer härleder mera och mera av sin beräkningskapacitet från SIMD vektorinstruktioner. Avhandlingen undersöker effekten denna typ av vektorinstruktioner har på ett LB program som körs på både vanliga Xeon processorer samt på Xeon Phi mångkärnsacceleratorer. Detta inkluderar en ingående analys av vilka optimeringstekniker som använts på Xeon Phi systemet för att få maximal prestanda. Speciellt viktigt var hur det snabba minnet används. Hur data ordnas i minnet och hur data manuellt skall läsas in en tid före det behövs är grundläggande för att utnyttja minnesbandbredden i dessa system effektivt.

## Acknowledgements

First off, I would like to thank both professor Jan Westerholm and doctor Keijo Mattila, your help has been invaluable both in preparing this thesis as well as the articles presented here. Secondly, I would like to thank professor Erik Lindahl and doctor Derek Groen for as acting as one of the reviewers, additionally I am grateful that professor Lindahl agreed to act as my opponent for the thesis defense. Everyone who worked at the HPC lab during my time have also been very supportive and deserves a mention.

Finally, I would like to thank all my friends and family that have put up with me being antisocial and not having time to do things since I had to "work on my thesis".

> Esbo, March 2018 Fredrik Robertsén

### List of original publications

- I F. Robertsén, K. Mattila, and J. Westerholm. Lattice Boltzmann method on GPUs: a comparison between OpenACC and CUDA. Submitted 2016

- II F. Robertsén, J. Westerholm, and K. Mattila. Lattice Boltzmann simulations at petascale on multi-GPU systems with asynchronous data transfer and strictly enforced memory read alignment. In 2015 23rd Euromicro International Conference on Parallel, Distributed, and Network-Based Processing, pages 604–609. IEEE, mar 2015

- III F. Robertsén, J. Westerholm, and K. Mattila. Designing a graphics processing unit accelerated petaflop capable lattice Boltzmann solver: Read aligned data layouts and asynchronous communication. The International Journal of High Performance Computing Applications, 31(3):246-255, aug 2016

- IV F. Robertsén, K. Mattila, and J. Westerholm. High-performance SIMD implementation of the lattice-Boltzmann method on the Xeon Phi processor. Concurrency and Computation: Practice and Experience, 2018. Minor revision Jan 2018

# List of co-authored publications not included in the thesis

• K. Mattila, T. Puurtinen, J. Hyväluoma, R. Surmas, M. Myllys, T. Turpeinen, F. Robertsén, J. Westerholm, and J. Timonen. A prospect for computing in porous materials research: Very large fluid flow simulations. *Journal of Computational Science*, 12:62 – 76, 2016

## Contents

| Inti | roduction                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Author's contributions                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                                                                                         | <b>5</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1  | Hardware trends of modern compute clusters and supercom-                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | puters                                                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.1.1 CPUs                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                                                                                         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.1.3 Xeon Phi                                                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.1.4 Interconnects $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2  | Programing models                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.2.1 OpenMP                                                                                                                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.2.2 Vectorization $\ldots$                                                                                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.2.3 CUDA programming                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.2.4 OpenACC                                                                                                                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The  | e lattice Boltzmann method                                                                                                                                              | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1  | Lattice Boltzmann theory                                                                                                                                                | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2  | Algorithms and implementation techniques                                                                                                                                | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.2.1 Lattice site addressing                                                                                                                                           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.2.2 Two-step algorithm                                                                                                                                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | -                                                                                                                                                                       | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.2.5 AA algorithm                                                                                                                                                      | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.2.6 Algorithm summary and applicability                                                                                                                               | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3  |                                                                                                                                                                         | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.4  |                                                                                                                                                                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.4.1 Data layouts                                                                                                                                                      | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Sim  | plified GPU programming with OpenACC                                                                                                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                                         | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.2  |                                                                                                                                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3  | Performance                                                                                                                                                             | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | <ol> <li>1.1</li> <li>Hig</li> <li>2.1</li> <li>2.2</li> <li>The</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Simu</li> <li>4.1</li> <li>4.2</li> </ol> | High performance computing         2.1 Hardware trends of modern compute clusters and supercomputers         2.1.1 CPUs         2.1.2 Nvidia GPUs         2.1.3 Xeon Phi         2.1.4 Interconnects         2.1 OpenMP         2.2.1 OpenMP         2.2.2 Vectorization         2.2.3 CUDA programming         2.2.4 OpenACC         2.2.4 OpenACC         3.1 Lattice Boltzmann method         3.1 Lattice Boltzmann theory         3.2 Algorithms and implementation techniques         3.2.1 Lattice site addressing         3.2.2 Two-step algorithm         3.2.3 Two-lattice algorithm         3.2.4 Swap algorithm         3.2.5 AA algorithm summary and applicability         3.3 Simple estimate of the performance potential of the LBM         3.4.1 Data layouts         Simplified GPU programming with OpenACC         4.1 Lattice Boltzmann GPU implementation         4.2 Lattice Boltzmann GPU implementation |

|    | 4.4          | Conclusion                                                    | 44              |  |

|----|--------------|---------------------------------------------------------------|-----------------|--|

| 5  |              | ge-scale parallel computing using the lattice Boltzmann       |                 |  |

|    |              | hod                                                           | 45              |  |

|    | $5.1 \\ 5.2$ | Input sample                                                  | $47 \\ 48$      |  |

|    | 5.2<br>5.3   | GPU data layout and algorithm performance $\dots \dots \dots$ | 48<br>49        |  |

|    | $5.3 \\ 5.4$ | I/O                                                           | $\frac{49}{52}$ |  |

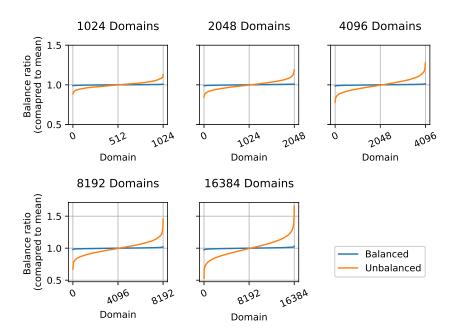

|    | -            | Load balance                                                  | $\frac{52}{55}$ |  |

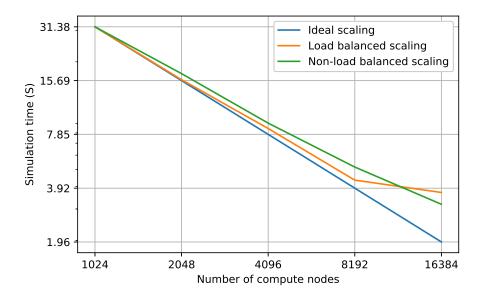

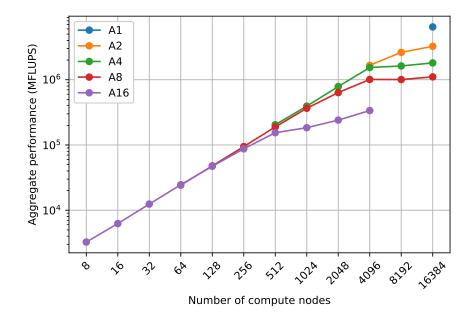

|    | 5.5          | Scalability                                                   |                 |  |

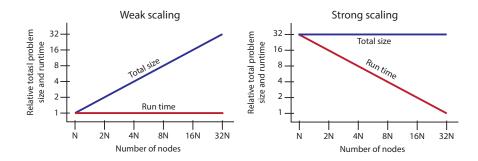

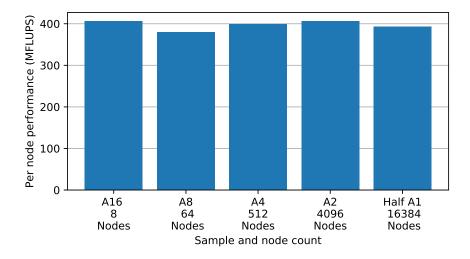

|    |              | 5.5.1 Weak scaling                                            | 56              |  |

|    |              | 5.5.2 Strong scaling $\ldots$                                 | 57              |  |

|    | F C          | 5.5.3 Scaling difficulties                                    | 58              |  |

|    | 5.6          | System utilization                                            | 59<br>60        |  |

|    | 5.7          | Scalability conclusion                                        | 60              |  |

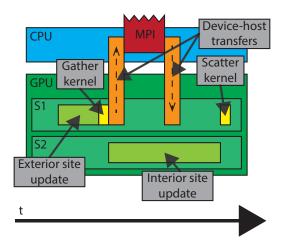

| 6  | Asy          | nchronous communication                                       | 61              |  |

|    | 6.1          | Dividing the computational domain                             | 63              |  |

|    | 6.2          | Removal of halo sites                                         | 64              |  |

|    | 6.3          | Performance of asynchronous communication                     | 65              |  |

|    | 6.4          | Asynchronous communication conclusion                         | 66              |  |

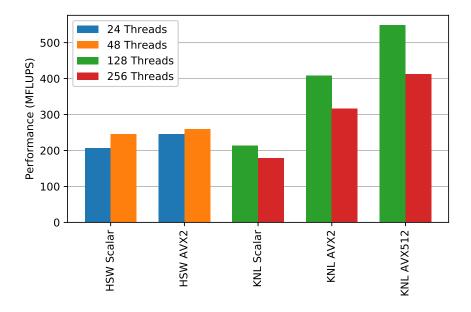

| 7  | Xec          | on Phi and vectorized lattice Boltzmann                       | 67              |  |

|    | 7.1          | Vectorized lattice Boltzmann                                  | 68              |  |

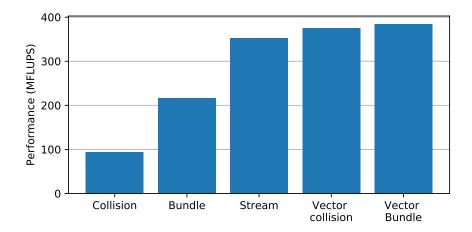

|    | 7.2          | Algorithm performance                                         | 71              |  |

|    | 7.3          | Thread count and vector length                                | 71              |  |

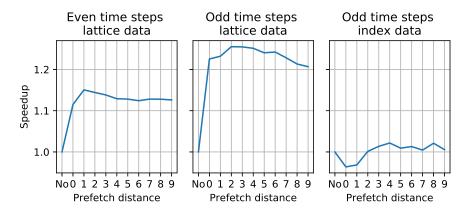

|    | 7.4          | Prefetching                                                   | 73              |  |

|    | 7.5          | Data layout                                                   | 74              |  |

|    | 7.6          | MCDRAM and NUMA modes                                         | 75              |  |

|    | 7.7          | Streaming stores                                              | 77              |  |

|    | 7.8          | Conclusion                                                    | 78              |  |

| 8  | The          | e lattice Boltzmann method, a petaflop and beyond             | 81              |  |

| 9  | Cor          | nclusion                                                      | 85              |  |

| Pa | Paper I      |                                                               |                 |  |

|    |              |                                                               |                 |  |

### Chapter 1

### Introduction

Computational fluid dynamics (CFD) [6], the process of mathematical modelbased computer simulation of fluid flows, enables researchers to analyze fluid flow phenomena in great detail. CFD allows hypothetical systems and systems that cannot be observed otherwise to be analyzed. For instance, if an airplane manufacturer wants to know how certain modifications to the wings of an airplane will perform, there is no need to build a scale model of the wings for all the modifications they want to try. Instead the manufacturer can design computer models of the wings and feed them into a CFD program that will simulate how the air moves around the wings. Not only is this easier and cheaper, since no physical manufacturing is needed, it also enables the engineers working on the problem to try countless small modifications to the wings without having to build a new physical model each time. Even though CFD greatly simplifies the design process, no matter how large the computing resources we have are, a simulation can only be as realistic as the underlying mathematical model. Before putting the wing into production there is still some real wind tunnel tests that need to be carried out.

With the need to run multiple simulations, the speed that these simulations can be run at becomes a key factor. Usually, these simulations require powerful workstation computers or clusters of computers working together for the solution to be available within a reasonable time. To achieve the results requires that the resources used are utilized to the fullest and that the simulation code is optimized for the computer system used.

There are fields where the researchers and engineers are trying to do the most with the resources they have at their disposal. A good example comes from the racing world of F1, where to keep costs down, the teams' computing resources are limited to a 25 teraflop system by the rules [7, 8]. That is, they can run a system that can do  $25 \times 10^{12}$  double-precision floating-point operations per second. This forces the teams and application developers to

optimize their codes and the way the resources are used in order to maximize the number of simulations can be done with the limited resources available.

At the other end of the spectrum we have the supercomputer systems used for scientific research, which have grown more and more powerful each generation. The challenge with these systems is to be able to scale the simulation to run on a significant part of the machine, and still run the simulation at a satisfactory performance. Currently, as of November 2017, the largest system in the world is just below 100 petaflops [9]. With faster systems being planned and built, some centers are aiming for exaflops machines, that is machines capable of 1000 petaflops, by 2020 [10]. Scaling programs to these new machines is by no means a trivial task. With the rise of accelerated computing and more customized architectures, even being able to utilize these machines might require large modifications to existing codes.

Fluid dynamics are also used in more time-critical situations. One such example comes from the University College London group that is attempting to use the lattice Boltzmann method to simulate the blood flow in the human brain [11]. The goal is to improve the way aneurysms are treated. For this, they need to be able to run their simulations in conjunction with the treatment, requiring the simulations to be done in a short amount of time.

This thesis covers our work on a highly scalable lattice Boltzmann CFD solver. It describes the work that allowed the solver to efficiently use computational accelerators to significantly increase the performance of the solver, as well as the work carried out that allowed the solver to efficiently use what was, at the time, the second most powerful supercomputer in the world.

The thesis is structured as follows: in chapter 2.1 we present the hardware of modern supercomputers and clusters and discuss how these have evolved over the past years. Chapter 2.2 covers the different programming methods used within the thesis, and gives some basic examples of these methods. The basic theory behind the lattice Boltzmann method is presented in chapter 3 and continues with the algorithms used to turn the theory into program code. A discussion about the factors likely to limit the performance of the solver is also included in the chapter.

Chapter 4 presents the first original research paper and discusses how the programming of GPUs can be made easier using the OpenACC programming standard. Chapter 5 covers how well the GPU-accelerated LB solver could scale on the Titan supercomputer and what to take into consideration when scaling an LB solver to such large machines. Chapter 6 covers how we implemented asynchronous communication and how that improves the performance of the GPU-accelerated LB solver. The use of Xeon Phi manycore accelerators, as well as vectorization of the LB solver, is discussed in chapter 7. Finally, chapter 8 discusses considerations that should be made for large scale LB simulations and how these simulations can be carried out on current supercomputer systems.

### 1.1 Author's contributions

All the articles in this thesis were made in cooperation with Dr. Keijo Mattila and Professor Jan Westerholm. The author's responsibility was developing the ideas for the articles, implementing and optimizing any code needed and carrying out simulations to gather data for the article. Dr. Mattila contributed with the theoretical background for the lattice Boltzmann method. Both Dr. Mattila and Prof. Westerholm helped in preparing the articles for publication.

### Chapter 2

### High performance computing

High performance computing refers to the use of parallel computing resources to run programs at a faster speed than a single workstation computer is capable of [12]. These parallel computing resources come in the form of clusters of computers connected with a high-speed network or supercomputers, which are effectively more purpose-built clusters. This chapter covers the hardware used in current HPC systems, as well as the programming methods for these systems.

### 2.1 Hardware trends of modern compute clusters and supercomputers

The TOP500 list [13] is used to rank the performance of supercomputers around the world. The performance is measured by how many floatingpoint operations the machines can perform per second while running the Linpack [14] benchmark. All systems currently on the list are based on some form of distributed system with multiple compute nodes connected to each other over a fast network. Most of the systems employ regular server CPUs for their computational power. The most widely deployed ones are Intel's commodity server CPUs, but also processors from AMD, IBM, Sun, or for some machines even completely customized chips are used.

On the CPU side, there has been a steady increase in the core count with each generation. Currently, the most ubiquitous are the 12 core CPUs as of November 2017 [13], while the maximum core count purchasable for an Intel server CPU is 28 cores and AMD offers up to 32 cores. As the core count grows, the frequency tends to drop for each core added [15]. With the lower frequency and higher core counts, parallelism of the code being run becomes a more crucial factor. Any part of the code that cannot be fully parallelized

will have its performance hurt by the lower clock frequency. Fortunately, the CPUs still retain higher boost clock frequencies when only a few cores are occupied, which helps serial sections of the code.

The most recent revolution in the HPC world has been the use of computational accelerators, which are used to add additional floating-point performance to the compute nodes. Accelerators usually come in the form of general purpose graphics processors (GPGPU) [16] and manycore processors [17], but also some custom floating-point accelerators are used [18]. These accelerators are specifically designed to deliver substantial amounts of floating-point performance. Since these rely on large amounts of parallelism, and in some cases larger vector units for their performance, it does limit their usage for normal datacenter tasks like for instance, serving web pages.

#### 2.1.1 CPUs

Since the introduction of the first dual core CPU system to the TOP500 list in 2002 [19], the Power4 CPU from IBM, there has been a steady increase in the core counts of the processors used in supercomputers. Adding the fact that the most common configuration currently is to use two or more CPUs per node, the parallelism of a single node has been increasing significantly. With a higher core count, there has also been a slow decrease in the frequency of the processors to keep the power consumption of the processor manageable. This puts a larger burden on the programmers to be able to efficiently parallelize their code to utilize the resources within a node.

The memory bandwidth available for each socket in a system has been increasing with newer revisions of the DDR memory standard and the increase in the frequency of the memory. The number of memory channels connected to each socket also increases the available bandwidth for the CPU. With the introduction of the Skylake CPUs [20], Intel went from 4 to 6 memory channels per socket. The AMDs Zen [21] architecture uses 8 channels per socket, providing up to 341 GB/s of theoretical memory bandwidth for a dual socket system. This is a substantial increase compared to 136GB/s for a dual socket Haswell [22] system and 256 GB/s for a dual socket Skylake system. From the Ivy bridge [23] generation up to the newest Skylake generation of Intel CPUs each socket can support 768 GB or, with some special CPU variants supporting up to 1.5 TB of memory, and AMDs Zen generation CPUs supporting up to 2 TB per socket.

The modern CPU core has evolved to be good at running a wide variety of different codes. As such, the cores of a modern CPU have large and complex cache hierarchies, with three or even four levels of cache between the CPU and the main memory [24]. These caches are significantly faster than the main memory of the system and are used as, among other things,

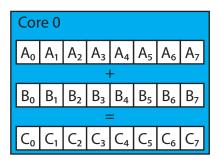

Figure 2.1: An illustration of how SIMD vectorization is used to parallelize an operation. Each vector, A and B, contains 8 values, which are added elementwise into C with one instruction

temporary storage and a buffer between CPU and memory. To reduce the observed latency for reading from the main memory, data is prefetched into the cache hierarchy. The prefetching works by the processor trying to identify the access pattern used by the program and predicting what data will be needed next and moving that into the cache structure ahead of time.

In addition to containing multiple processing cores, modern CPUs use simultaneous multithreading (SMT) [25] to allow multiple threads to run in the same core at the same time. The idea is to have multiple threads that can use any resources that the other threads do not currently use. This allows for a better utilization of the resources within a core. Mainstream Intel and AMD processors currently both support 2-way SMT. The modern CPU cores are also able to perform out of order execution, where the order that the instructions executed are issued is based on when the operands for the operations are available, instead of the order they are in the program code.

To further increase the performance and parallelism of the CPUs, vector instructions in the form of SIMD (Single Instruction Multiple Data) instructions are used [26]. These allow a single core to operate on multiple data values with one instruction as illustrated in figure 2.1. The current generation mainstream SIMD instructions support 256-bit vectors using the AVX2 instruction set [27]. With AVX2, the core can process 4 double-precision floating-point values at once. The current generation of server and HPC specific processors use 512-bit vectors, with the AVX-512 instruction set [28]. The AVX-512 instruction set enables those processors to process 8 double-precision floating-point values with one instruction. To use these instructions, the computation performed needs to be expressed in a form that allows the use of these instructions.

There is some support from the compiler to automatically vectorize the code, but this relies on the compiler to be able to identify which parts of the computation can be vectorized and to guarantee that vectorizing these parts does not change the result of the computation. Guaranteeing vectorization usually involves rewriting the program to explicitly use the vector instructions or at least adding hints for the compiler as to which sections should be vectorized and what data dependencies exist within the program.

#### 2.1.2 Nvidia GPUs

A more recent addition to the HPC field has been the introduction of computational accelerators, hardware designed specifically to accelerate the processing of floating-point operations. As a concept this is nothing new. The original x87 FPU was already a floating-point accelerator. However, modern accelerators in HPC are massively parallel processors that are especially designed for floating-point performance. Currently, the most widely used accelerators in use in the HPC world are GPGPUs, with the clear majority being Nvidia Tesla accelerators.

The GPGPUs have their roots in the processing of real time computer graphics for computer games, rendering the 3D graphics shown on the screen in real time. The rendering methods used for real time computer graphics are massively parallel operations that rely heavily on floating-point arithmetic. Combined with the growing screen resolution and improved graphics quality, this has led to the GPU evolving into a massively parallel processor specialized in floating-point math. The first GPGPU widely used within the HPC community had a few hundred simple CUDA cores, but as on the CPU side, the core count has grown significantly as newer GPUs are released, with current GPUs having over 3000 simple CUDA cores [29].

Even though the GPUs have many cores, these are not the same kind of cores that are found in regular CPUs, the CUDA cores are far simpler. The cache structure on the GPU is also simpler and shallower and mostly used as a coalescing buffer [16]. The GPU cores come with some limitations. The cores cannot all operate independently, which means that they are unable to each run a unique instruction every clock cycle. On the GPU, the cores are arranged into larger groups of cores referred to as a streaming multiprocessor. The Pascal generation uses 64 cores per multiprocessor that can perform single precision operations and 32 cores that can perform double precision operations [29].

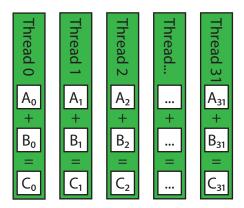

The parallelism within the GPU is based on the SIMT (Single-Instruction, Multiple-Thread) paradigm [16], where multiple threads are executing the same instruction at the same time. This is a comparable way to the SIMD vectorization of regular CPUs. The difference from SIMD is that in the SIMT case there are multiple cores performing the operation for the data within the vector, instead of one core running the instruction. In the case

Figure 2.2: An illustration of how multiple threads in a GPU execute the same instruction in different values. Each thread adds together one value, A and B, and stores the result in C

of the Nvidia GPUs, the threads are executed in groups of 32 [16], referred to as a warp. This warp is then executed on the cores within a multiprocessor. All cores that are working on the same warp are executing the same instruction but on different data. If there is divergence in the execution between the threads, the different branches will be serialized. The serialization reduces the performance, since it still requires all cores within the warp to participate [16].

Another feature that the GPUs carried over from the graphics world is that they offer greater memory bandwidth than a normal CPU based system. The recent Nvidia GPUs can deliver over 700GB/s [29] of theoretical memory throughput. The memory bandwidth comes at the price of space, with most of the GPUs used for HPC today having between 12 and 16 GB of on board memory per GPU.

One of the major drawbacks of the GPGPU accelerators is that they are added to the compute nodes as PCI-e or SXM2 [30] add-in cards. Since the GPUs are add-in cards and cannot host themselves, they need a host system to function, effectively a compute node with a normal CPU. As add-in cards, the bus they are connected to limits the amount of bandwidth available for communication between host and GPU, and between different GPUs in the system. In the case of PCI-e cards, the maximum theoretical bandwidth is limited to 16 GB/s [31]. To improve this situation, Nvidia introduced a high-speed interconnect, NVLink [29] capable of 20-25 GB/s of bandwidth per port, which can be used to communicate between GPUs in the system. The NVLink interconnect can also be used to communicate with the host CPU in certain systems where the host CPU supports an NVLink connection [32].

#### 2.1.3 Xeon Phi

The Xeon Phi line of manycore accelerators follows a similar design as the GPUs. They simplify the cores and pack more of them on to the chip. Unlike the GPU, these do not have thousands of cores. The first generation, codenamed Knights corner (KNC) [33], had up to 61 cores. The second-generation Xeon Phi processors, codenamed Knights landing (KNL) [34], have core counts between 64 and 72 cores. To further increase the number of threads that can run the Xeon Phi, it supports up to 4-way SMT. Instead of relying on a large core count for their performance, these use 512-bit wide vectors to achieve a higher floating-point arithmetic performance than regular CPUs can achieve.

The first generation Xeon Phis did not see wide adoption due to the difficulties of getting performance from the programs running on it [35, 36]. The second generation improved on a lot of the issues compared with the first generation. Instead of using a proprietary instruction set like the KNC generation, the KNL generation uses a subset of the AVX-512 instruction set [37]. It can also run code from older vector instruction sets, and in fact the KNL processor can directly run binaries built for regular Xeon CPUs. The KNL generation also moves away from being an add-in card that requires a host system, like the KNC generation, into a self-hosted system where the KNL processor is the only processor in the system [37]. Another substantial change is the move away from a ring bus used as the core-to-core interconnect on the KNC generation, to a mesh network. This mesh network improves the core-to-core communication. Within each node in the mesh network sits two cores that share the same L2 cache and the same connection to the network. The memory controllers, both the high speed MCDRAM and regular DDR memory, are connected to the same mesh.

As with the GPUs, the Xeon Phi processors employ a small amount of fast memory to accelerate memory bound computation. The KNC generation uses GDDR5 memory, the same memory as used by contemporary GPUs. The latest KNL generation uses 16 GB of MCDRAM capable of delivering over 450GB/s [34] of memory bandwidth. A KNC processor is also able to support standard DDR4 memory to enable it to run programs requiring more than 16GB of memory. The MCDRAM on these can be used in multiple modes. One alternative is to use it as a large last level cache that is transparent from the view of the programmer. Data from the MC-DRAM cache is accessed at a higher bandwidth than what is available from the DDR4 memory space. Another mode is to use it as a separate memory space, using special allocation functions and only placing certain structures of the program in this faster memory.

#### 2.1.4 Interconnects

Current HPC systems use many technologies that exist in a regular datacenter. The difference between HPC systems and those serving for instance web pages is that the HPC systems are balanced differently. HPC system focus on delivering the maximum floating-point performance in a specific power and size envelope. HPC system also tend to use more advanced networks to connect the nodes to each other. The node-to-node interconnects used for HPC systems are set up to deliver higher bandwidth than those usually found in regular data centers, and are designed to be capable of delivering low latency communication.

The network topology, the way the nodes are arranged and connected to each other in HPC systems, is often done to maximize the amount of bandwidth available between two given nodes in the system. Common topologies include fat tree topologies, cube, and torus topologies but also more exotic layouts such as the dragonfly topology [38]. While the November 2017 TOP500 list does include a little over 200 systems using commodity 10 gigabit ethernet, the top systems all use more exotic interconnects. InfiniBand [39], being the most widely used HPC focused network on the list, and Omnipath [40] networks can both be used to build a cluster with off the shelf components, and are available from multiple server vendors.

Another interconnect option for HPC systems is to use one of the custom interconnects available from some more HPC-focused server vendors. These are available from vendors such as Cray, with their Aries [41] network used in the XC line of supercomputers and the Tofu interconnect used by Fujitsu for the K computer [42]. These custom interconnects attempt to deliver even greater bandwidth and lower latencies to all the nodes, even when scaling up the systems to thousands of compute nodes.

#### 2.2 Programing models

The recent evolution in modern supercomputer systems is the addition of more and more parallelism within a node, instead of scaling up the number of compute nodes, leading to the programming of these systems becoming more complex [43, 44]. Traditionally, HPC codes have relied heavily on the message passing model of parallelism, usually implemented using MPI [45]. This model is based on processes that all have their own memory space and run code serially. The processes communicate with each other by sending and receiving messages. With this model, parallel execution is achieved by running multiple processes. The drawback of this model is that as the number of cores in the system increases, so does the number of processes, making it harder to manage. The amount of communication needed also increases, which can affect scaling. Memory usage is another big drawback of this approach. Since all processes have their own memory space they all need their own copies of any shared memory structures.

MPI cannot be used on GPUs, since the GPUs require other parallelism paradigms. To reduce the amount of MPI communication needed and to enable the use of computational accelerators, HPC programs are moving to a hybrid parallelism model [46, 47, 36]. This means that programs employ MPI together with some other form of parallelism. This second level of parallelism can be accelerator specific languages, to enable the use of accelerators, but also shared memory parallelism [48] within a compute node. This allows the program to cut down on the number of MPI processes needed to efficiently use the resources available.

#### 2.2.1 OpenMP

OpenMP [49] is one of the more popular APIs for shared memory parallelism and most of the mainstream compilers have support for it [50]. OpenMP gives the ability to implement varying degrees of parallelization, such as a simple data parallel for loop, where the iterations of the loop are executed in parallel. OpenMP is also able to do more complex task-based parallelism where threads are spawned with the goal of completing a section of code in parallel with either the main thread or other tasks.

In OpenMP, parallelism is described using simple compiler directives inserted by the programmer into the program code. The use of directives makes it easy to modify existing code without major changes to the code, in the case the algorithms and methods used can be parallelized in that way. Since OpenMP only uses compiler directives to parallelize the code it is still possible to compile the code as a single threaded application. Sections of code we want to execute in parallel are described as basic blocks starting with a **#pragma omp parallel** directive. Within the block, execution is performed in parallel by all active threads, and at the end of the section there is an implicit synchronization guaranteeing that all threads have finished. After the block, only one thread will be left to continue the execution of the program until another parallel section is encountered.

Listing 2.1 illustrates how simple data parallelism can be expressed using OpenMP, in this case the addition of two arrays. The goal in parallelizing this example is that the addition within the loop will be executed in parallel. Memory allocation and initialization has been excluded for the sake of simplicity. The **#pragma omp parallel** directive has been combined with a **#pragma omp for** directive to indicate to the compiler that the iterations of the loop should be parallelized. The work within the loop is then distributed according to the schedule used. In this case the default static scheduling is used, which statically divides the loop iterations by the number of treads. More complex scheduling, such as various kinds of dynamic scheduling, is also available. Dynamic scheduling enables the load of the loop to be more evenly distributed, in case the iterations require a different amount of work. This scheduling gives rise to some additional computational overhead because the distribution of work among the threads itself requires some effort. When parallelizing a loop using OpenMP, it is up to the programmer to guarantee that there is no dependency between the iterations of the loop. Any dependencies could cause race conditions between the threads and thus affect the correctness of the code.

Listing 2.1: Code example that shows how the addition of two arrays can be parallelized with OpenMP

#### 2.2.2 Vectorization

Vectorization using the single instruction multiple data (SIMD) paradigm refers to the concept of having one instruction, apply the same operation to multiple values at the same time. The length of these vectors varies with CPU type and generation. The widest vectors used in modern x86 CPUs are 512-bit in Xeon Phi manycore processors [37] and the Skylake generation of regular Intel Xeon processors [37]. The 512-bit vectors give the processor the ability to process 8 double-precision or 16 single-precision values with a single instruction.

The vector instructions form a separate instruction set from the regular scalar instructions of the CPU. To use the vector functionality, the compiler needs to generate vector instructions for the code. Ideally the compiler can identify which sections of the code can be vectorized. However, automatic vectorization relies on the compiler being able to identify which sections can be vectorized and that the compiler can guarantee that vectorizing the code will not change the result, something that is not always possible to do. In cases where the compiler is unable to vectorize the code, the programmer may need to modify the code in such a way that the compiler can vectorize it.

One approach to guarantee vectorization is to use OpenMP directives to control what parts of the program are vectorized. Since version 4.0 [51], vectorization can be described in the same way as multithread parallelism is expressed using OpenMP. A **#pragma omp simd** statement can be used to indicate to the compiler that the code should be vectorized. The compiler directives can also be used to circumvent the checks done by the compiler to guarantee correct results of the vectorized code. This is useful in the case where the programmer knows that vectorizing the code will not affect the result but the compiler is unable to detect this. One drawback here is that the vectorization still relies on the compiler to generate the vector instructions, and as such it might not be possible to vectorize computation that requires transformations the compiler is unable to perform.

Finally, vectorized code can be manually generated using intrinsic functions, as shown in listing 2.2. These functions are wrappers to specific machine instructions. Using these guarantees that the execution will be vectorized. Using intrinsic functions has the drawback of making the code seem complex, since the regular operations between operands are replaced with function calls. The intrinsic functions also limit the vectorization to one specific instruction set. One way of improving this is to use a vector math library or a compiler which defines the regular arithmetic operations for the vector types as well. With these vector libraries, vectorized code can be written in much the same way as scalar code, but the code is guaranteed to be vectorized.

Listing 2.2: A code example showing how the addition of two arrays can be vectorized using AVX vector instructions

```

double *a, *b, *c;

for (int i = 0; i < count; i = i+vecLen){

__m512d aV = _mm256_load_pd(&a[i]);

__m512d bV = _mm256_load_pd(&b[i]);

__m512d cV = _mm256_add_pd(aV, bV);

_mm256_store_pd(&c[i], cV);

}

```

#### 2.2.3 CUDA programming

CUDA was introduced by Nvidia in 2007 [16] as a programming language that allows the use of Nvidia graphics processors for general purpose computing tasks. CUDA gives the ability to easily express the parallelism needed to efficiently offload the computation to a GPU from Fortran and C/C++ code. CUDA is often considered a low-level language when it comes to GPU programming, since it gives the programmer great control over how and what the GPU executes and fine control over what data is transferred to and from the GPU and how it is transferred.

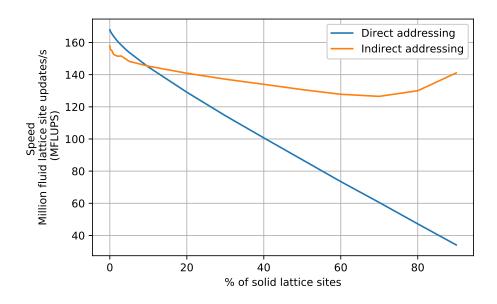

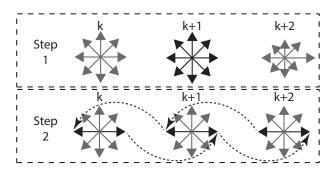

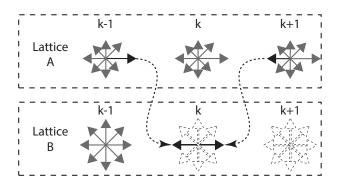

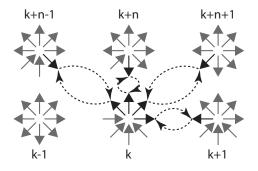

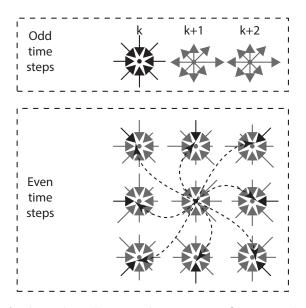

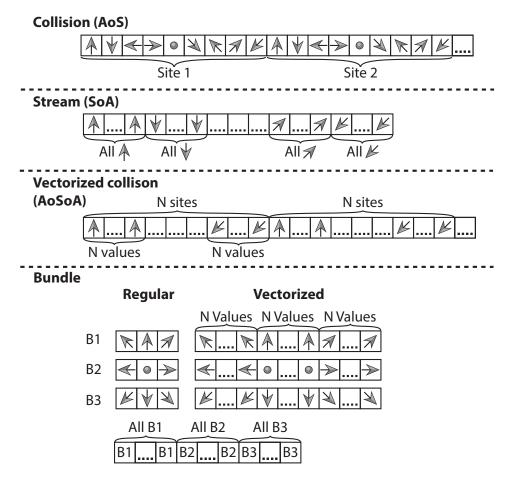

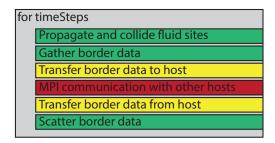

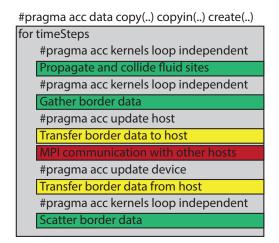

The code that will be run on the GPU needs to be described in terms of CUDA kernels. The kernel contains the code that will be executed by each thread running on the GPU. When converting code that has previously been parallelized with the help of OpenMP, the kernel code is the same code which was in the loop body that was parallelized with OpenMP. The loop iteration variable is replaced with a thread id, computed from the thread block and grid ID numbers.